Commissioning AKT2G-ENC-190-000

Jump to a section on this page:

Normal Operation Mode

Process data and modes - Normal Operation Mode

In AKT2G-ENC-190-000 “normal operation mode” the following modes are available:

| Mode | Distributed Clock | Main PDO |

Comment | Optional PDO 1 | Comment | Features CoE | Comment |

|---|---|---|---|---|---|---|---|

|

1 |

Operational |

0x1A00 + 0x1600 |

Byte-Alignment |

0x1A02 |

Frequency: 32 bit Period: 16 bit Window: 16 bit CoE object 0x8001:02 |

0x8000:01 + 0x8001:02 |

Register reload + Reload Value |

|

2 |

Operational |

" |

" |

" |

" |

0x8000:02 |

Index Reset |

|

3 |

Operational |

" |

" |

" |

" |

0x8000:03, :04, :05 |

FWD Cnt + pos/ neg Gate |

|

4 |

Operational |

0x1A01 + 0x1601 |

16 bit Value/Latch Word Alignment |

0x1A02 |

Frequency: 32 bit Period: 16 bit Window: 16 bit CoE object 0x8001:02 |

0x8000:01 + 0x8001:02 |

Register reload + Reload Value |

|

5 |

Operational |

" |

" |

" |

" |

0x8000:02 |

Index Reset |

|

6 |

Operational |

" |

" |

" |

" |

0x8000:03, :04, :05 |

FWD Cnt + pos/ neg Gate |

-

-

Frequency

- The timeframe for the frequency calculation is set to 10 ms (see Fig. “Process data” tab); in addition a variably configurable measuring window is available (parameterization via object 0x8001:01, output frequency value in object 0x6000:06).

- Only the increment edges in the specified time window are counted.

- If no edge change occurs for approx. 1.6 s, any frequency specification is cancelled.

- This calculation is carried out in the slave without reference to the distributed clocks system. It is therefore independent of the DC mode.

- No frequency measurement is possible if the counter is blocked by the gate. In this case the period can be measured regardless.

- If an encoder signal is only present at input A/A and the frequency/period is to be measured, the terminal must be set to “Enable FWD count” in CoE 0x8000:03.

- A C or external reset restarts the frequency measurement. The last frequency value remains unchanged until a new frequency value is determined.

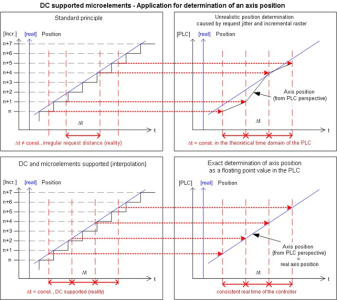

Figure 8-32: Frequency measurement principle in normal operation mode

Period calculation

- This calculation is carried out in the slave without reference to the distributed clocks system. It is therefore independent of the DC mode.

- In each cycle the interval between 2 positive edges of input A is counted with a resolution of 100 ns.

- If no edge change occurs for approx. 1.6 s, any period specification is canceled.

-

-

-

Frequency and period measurement

From the explanatory notes above it is apparent that the frequency measurement can measure the current axis status (velocity) significantly more accurately than the period measurement. Frequency measurement is therefore preferable, if possible.

-

Register Reload

- If Register Reload is enabled in CoE object 0x8000:01, the counter value is set to zero in the event of overflow over the value in CoE object 0x8001:02 and to the value in CoE object 0x8001:02 in the event of underflow below 0.

Index Reset

- If Index Reset is enabled in CoE object 0x8000:02, input C resets the counter to 0.

"Register Reload" and "Index Reset"

"Register Reload” and “Index Reset” cannot be operated simultaneously.

FWD Cnt

- If FwdCnt is activated in CoE object 0x8000:03, the AKT2G-ENC-190-000 operates as counter on channel A. Channel B indicates the counting direction: B=TRUE forward, B=FALSE backward. The counter can be locked via the gate input (24 V).

- CoE object 0x8000:04 (TRUE): Locking of the counter at the gate input with positive edge (0 V -> + 24 V).

- CoE object 0x8000:05 (TRUE): Locking of the counter at the gate input with negative edge (+ 24 V -> + 0 V).

Object Description and Parameterization - Normal Operation Mode

Restore object

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

1011:0 |

Restore default parameters |

Restore the default settings |

UINT8 |

RO |

0x01 (1dec) |

|

1011:01 |

SubIndex 001 |

If this object is set to “0x64616F6C” in the set value dialog, all backup objects are reset to their delivery state. Note: Some FW versions also accept the following input: "0x6C6F6164". |

UINT32 |

RW |

0x00000000 (0dec) |

Configuration data

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

8000:0 |

Non-Volatile Settings 0 |

Maximum subindex |

UINT8 |

RO |

0x05 (5dec) |

|

8000:01 |

Enable register reload |

The counter counts up to the “Counter reload value”, or the “Counter reload value” (0x8001:02) is loaded in the event of an underflow Example 360° encoder with set bit: Moves in positive direction via Counter reload value: Reset counter value to 0. Moves in negative direction less than 0: Reset counter value to Counter reload value |

BOOLEAN |

RW |

0x00 (0dec) |

|

8000:02 |

Enable index reset |

Activates input “C” for resetting the counter. Example 360° encoder with set bit: Moves in positive direction (signal at input “C”): Reset counter value to 0 Moves in negative direction (signal at input “C”): underflow with FFFF, FFFE etc.) |

BOOLEAN |

RW |

0x00 (0dec) |

|

8000:03 |

Enable FWD count |

FALSE The terminal operates in quadrature decoder mode TRUE The terminal operates as counter, count direction to input B |

BOOLEAN |

RW |

0x00 (0dec) |

|

8000:04 |

Enable pos. gate |

Gate input responds to positive edge and locks the counter |

BOOLEAN |

RW |

0x01 (1dec) |

|

8000:05 |

Enable neg. gate |

Gate input responds to negative edge and locks the counter |

BOOLEAN |

RW |

0x00 (0dec) |

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

8001:0 |

Non-Volatile Settings 1 |

Maximum subindex |

UINT8 |

RO |

0x02 (2dec) |

|

8001:01 |

Frequency window |

The value specifies the size of the time window for the “Window” variable. resolution: 16µs; e.g. default value: 16 µs x 100dec = 1.6 ms |

UINT16 |

RW |

0x0064 (100dec) |

|

8001:02 |

Counter reload value |

If “Enable register reload” = TRUE, the counter counts up to this value and is loaded with this value in the event of an underflow |

UINT16 |

RW |

0xFFFF (65535dec) |

Input data

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

6000:0 |

Inputs |

Length of this object |

UINT8 |

RO |

0x06 (6dec) |

|

6000:01 |

Status |

Status byte |

UINT8 |

RO |

0x00 (0dec) |

|

6000:02 |

Value |

meter reading |

UINT16 |

RO |

0x0000 (0dec) |

|

6000:03 |

Latch |

Latch value |

UINT16 |

RO |

0x0000 (0dec) |

|

6000:04 |

Frequency |

Frequency value (resolution: 0.01 Hz / digit) [fixed 10 ms measuring window] |

UINT32 |

RO |

0x00000000 (0dec) |

|

6000:05 |

Period |

Period (resolution 500 ns / digit) |

UINT16 |

RO |

0x0000 (0dec) |

|

6000:06 |

Window |

Measured value of the variable timeframe ( “Frequency window” (0x8001:01) |

UINT16 |

RO |

0x0000 (0dec) |

Output data

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

7000:0 |

Outputs |

Length of this object |

UINT8 |

RO |

0x02 (2dec) |

|

7000:01 |

Ctrl |

Control byte |

UINT8 |

RO |

0x00 (0dec) |

|

7000:02 |

Value |

The counter value to be set via CNT_SET (CB.02). |

UINT16 |

RO |

0x0000 (0dec) |

Control and status byte

Control byte

The control byte (CB) is located in the output process image, and is transmitted from the controller to the terminal.

|

Bit |

CB.7 |

CB.6 |

CB.5 |

CB.4 |

CB.3 |

CB.2 |

CB.1 |

CB.0 |

|

Name |

- |

- |

- |

- |

EN_LATCH_EXTN |

CNT_SET |

EN_LATCH_EXTP |

EN_LATC |

| Bit | Name | Description | |

|---|---|---|---|

|

CB.3 |

EN_LATCH_EXTN |

1bin |

With a valid EN_LATCH_EXTN bit the counter value is stored in latch input (index 0x6000:03) when the first external latch pulse with falling edge is encountered. Subsequent pulses have no influence on the latch value. Please note: A new counter value can only be written to the latch input when the Latch Valid bit (LAT_EXT_VAL) in the status byte has a low signal level. |

|

CB.2 |

CNT_SET |

rise |

The counter is set with rising edge |

|

CB.1 |

EN_LATCH_EXTP |

1bin |

With a valid EN_LATCH_EXTP bit the counter value is stored in latch input (index 0x6000:03) when the first external latch pulse with rising edge is encountered. Subsequent pulses have no influence on the latch value. Please note: A new counter value can only be written to the latch input when the Latch Valid bit (LAT_EXT_VAL) in the status byte has a low signal level. |

|

CB.0 |

EN_LATC |

1bin |

The null point latch (C input) is activated. The counter value is saved when the first external latch pulse after a valid EN_LATC bit encountered (this has priority over EN_LAT_EXTN / EN_LAT_EXTP). If the bit is set subsequent pulses have no influence on the latch value. Please note: A new counter value can only be written to the latch input when the Latch Valid bit (LATC_VAL) in the status byte has a low signal level (the LATC_VAL bit (SB.0) is only cleared by the terminal when the C pulse = LOW). |

Status byte

The status byte (SB) is located in the input process image, and is transmitted from terminal to the controller.

|

Bit |

SB.7 |

SB.6 |

SB.5 |

SB.4 |

SB.3 |

SB.2 |

SB.1 |

SB.0 |

|

Name |

- |

- |

STATUS_INPUT |

OVERFLOW |

UNDERFLOW |

CNTSET_ACC |

LAT_EXT_VAL |

LATC_VAL |

| Bit | Name | Description | |

|---|---|---|---|

|

SB.5 |

STATUS_INPUT |

0bin/1bin |

Indicates the status of INPUT 1 |

|

SB.4 |

OVERFLOW |

1bin |

This bit is set if the 16-bit counter overflows (65535 to 0). It is reset when the counter exceeds one third of its measuring range (21845 to 21846) or immediately an underflow occurs. |

|

SB.3 |

UNDERFLOW |

1bin |

This bit is set if the 16-bit counter underflows (0 to 65535). It is reset when the counter drops below two thirds of its measuring range (43690 to 43689) or immediately an overflow occurs. |

|

SB.2 |

CNTSET_ACC |

1bin |

The data for setting the counter (index 0x7000:02 ) is accepted from the terminal. |

|

SB.1 |

LAT_EXT_VAL |

1bin |

An external latch pulse has occurred. The data with index 0x6000:03 match the latched value when the bit is set. To reactivate the latch input EN_LAT_EXTN or EN_LATCH_EXTP (CB.3 or CB.1) has first to be cleared and then to be set once more. |

|

SB.0 |

LATC_VAL |

1bin |

A zero point latch has occurred. The data with index 0x6000:03 match the latched value when the bit is set. In order to reactivate the latch input, it is necessary for EN_LATC (CB.0) first be cleared and then to be set once more. |

Single-Ended Connection for TTL Encoder

In addition to encoders with differential RS422 interface, single-ended encoders with TTL interface are also supported. Please note the following:

- Operating mode selection encoder "0x8000:03 Enable FWD count = FALSE".

- The differential inputs (/A, /B, /C) must remain open and must not be connected to ground

Enhanced Operation Mode

Process data and modes - Enhanced operation mode

In AKT2G-ENC-190-000 “enhanced operation mode” the following modes are available:

| Mode | DC | Main PDO | Comment | Optional PDO 1 | Comment | Optional PDO 2 | Comment | Features CoE | Comment |

|---|---|---|---|---|---|---|---|---|---|

|

7 |

0x1A04 + 0x1603 |

Count/Latch in 32 bit |

0x1A05 or 0x1A06 |

Frequency (32 bit) |

-- |

|

0x80n0:nn |

CoE combinations 0x80n0:nn |

|

|

8 |

" |

0x1A03 + 0x1602 |

compact: Count/Latch in 16 bit |

" |

" |

-- |

|

" |

" |

|

9 |

DC/DCi |

0x1A04 + 0x1603 |

Count/Latch in 32 bit |

" |

" |

0x1A07 or 0x1A08 |

Timestamp 32 bit (compact) |

" |

" |

|

10 |

" |

0x1A03 + 0x1602 |

compact: Count/Latch in 16 bit |

" |

" |

" |

" |

" |

" |

Frequency

- The time window for the frequency calculation and the resolution can be parameterized in CoE objects 0x80n0:11, 0x80n0:13, 0x80n0:15, 0x80n0:17.

- The positive edges of track A are counted within the specified timeframe and the next edge including the time up to it are counted. The waiting time can be set in CoE object 0x80n0:17 “Frequency Wait Time” (unit: ms). The default value is 1.6 sec. This is also the maximum value.

- The time window is 10 ms (default), min. 1 µs. With the default setting it is possible to measure frequencies up to approx. 800 kHz. At higher frequencies a smaller value must be selected for the timeframe.

- The time is measured with a resolution of 100 ns.

- This calculation is carried out in the slave without reference to the distributed clocks system. It is therefore independent of the DC mode.

- No frequency measurement is possible if the counter is blocked by the gate. In this case the period can be measured regardless.

- If an encoder signal only is only present at input A/A and the frequency/period is to be measured, the terminal must be set to “Up/Down Counter” in CoE 0x8010:03.

- A C or external reset restarts the frequency measurement. The last frequency value remains unchanged until a new frequency value is determined.

Frequency measurement

- Basic unit 1 µs: all window sizes

Measurement sequence

- The measurement starts with a positive edge at track A. The current counter value and time (resolution: 100 ns) are stored.

- After the measuring window time has elapsed (index 0x80n0:11), the system waits for the following rising edge at track A or a maximum of 1.6 sec or the time from 0x80n0:17

- The frequency is calculated from the edge difference and the actual elapsed time.

Period calculation

- This calculation is carried out in the slave without reference to the distributed clocks system. It is therefore independent of the DC mode.

- In each cycle the interval between 2 positive edges of input A is counted with a resolution of 100 ns.

- If no edge change occurs for approx. 1.6 s, any period specification is cancelled.

-

-

Frequency and period measurement

From the explanatory notes above it is apparent that the frequency measurement can measure the current axis status (velocity) significantly more accurately than the period measurement. Frequency measurement is therefore preferable, if possible.

Latch

Activation of latch C input (“C”) and saving (“latching”) of the counter value (index 0x70n0:01)

- The counter value is saved at the first external latch pulse (positive edge at input “C”) after the bit has been set (“TRUE”) in index 0x70n0:01 (has priority before 0x70n0:02 / 0x70n0:04). The subsequent pulses at the other inputs have no influence on the latch value in index 0x60n0:12 if the bit is set.

- Note for “Latch C valid” bit: A new counter value at the latch input can only be written once the value of the “Latch C valid” bit (index 0x60n0:01) is “FALSE”.

Activation of the external latch input (“gate/latch”) and latching of the counter value (index 0x70n0:02, 0x70n0:04)

- The counter value at the latch input (Index 0x70n0:02) will be saved upon the first external latch pulse with a rising edge if the bit (“TRUE”) is set in index 0x60n0:12. The subsequent pulses have no influence on the latch value in index 0x60n0:12.

- The counter value at the latch input (Index 0x60n0:12) will be saved upon the first external latch pulse with a falling edge if the bit (“TRUE”) is set in index 0x70n0:04. The subsequent pulses have no influence on the latch value in index 0x60n0:12.

- Note for "Latch extern valid" bit: A new counter value at the latch input can only be written once the value of the “Latch extern valid” bit (index 0x60n0:02) is “FALSE”.

Reset

- Counter reset (index 0x80n0:01, 0x80n0:02, 0x80n0:10): For a counter reset via input C set the bit in index 0x80n0:01, for a reset via the external latch input set the bit in index 0x80n0:02.

- The functions “Enable C reset” (0x80n0:01) and “Enable extern reset” (0x80n0:02) cannot be activated simultaneously.

- Note for “Extern reset polarity”, index 0x80n0:10: The edge for setting the counter to zero can be selected via index 0x80n0:10.

Bit not set: counter is set to zero with falling edge.

Bit set: counter is set to zero with rising edge.

Up/down counter

- The mode (encoder or up/down counter) is set via the CoE objects (profile-specific objects, tab CoE Online, index 0x80n0:03 “Enable up/down counter”). Click on the corresponding row of the index to be parameterized, enter 1 in the SetValue dialog and confirm with OK.

- Set the gate polarity accordingly via object 0x80n0:04.

- An additional option for reversing the rotation direction is available by setting the bit in index 0x80n0:0E.

Overflow/underflow

- Overflow/underflow control is inactive in combination with an activated reset function (C/external).

- The underflow bit (0x60n0:04) is set if an underflow ...00 →...FF occurs. It is reset if 2/3 of the counter range are underrun.

- The overflow bit (0x60n0:05) is set if an overflow FF...→ 00... occurs. It is reset if 1/3 of the counter range is exceeded.

Open circuit detection

- A separate open circuit detection can be activated for each of the channels A, B and C (index 0x80n0:0B, 0x80n0:0C, 0x80n0:0D).

- Open circuit detection is activated for channels A and B by default.

- A differential voltage of typically -1.5 V >Vid > +1.5 V is detected as an open circuit.

- If an open circuit is detected, it is indicated as process data open circuit = TRUE. The bit in object 0x60n0:07 is set. An open circuit is indicated separately in indices 0xA0n0:01 (track A), 0xA0n0:02 (track B) and 0xA0n0:03 (track C).

- TxPDO state also becomes TRUE if an open circuit is detected, since invalid data have to be assumed.

-

-

Open circuit detection vs. single-ended lines (TTL interface)

The open circuit detection does principally not work with single-ended lines (TTL interface).

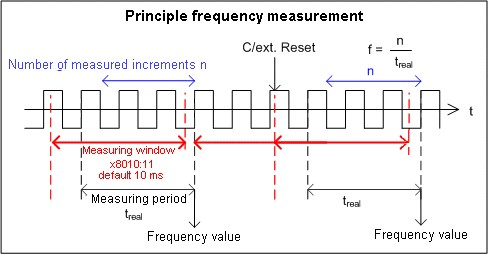

Micro-increments

- Works with and without distributed clocks, but this is only meaningful in conjunction with one of the DC modes

- By setting the counter value only the integer component can be modified.

- The principle:

Figure 8-33: Frequency measurement principle in enhanced operation mode

The highly constant query cycles (accuracy: 100 ns) of the distributed clocks systems enable the AKT2G-ENC-190 to interpolate axis positions between the counted encoder increments from a certain speed. The interpolation resolution is 8 bit, corresponding to 256 values. A standard encoder with 1,024 bars with 4way evaluation and micro-increments thus becomes a high-resolution axis encoder with 4096 * 256 = 1,048,567 bars.

Underrunning of the minimum velocity is indicated by the object 0x60n0:08 (extrapolation stall) in the process data.

Configuration Data

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

8010:0 |

ENC Settings |

Maximum subindex |

UINT8 |

RO |

0x17 (32dec) |

|

8010:01 |

Enable C reset |

The counter is reset via the C input. |

BOOLEAN |

RW |

0x00 (0dec) |

|

8010:02 |

Enable extern reset |

A counter reset is triggered via the external latch input (24 V) |

BOOLEAN |

RW |

0x00 (0dec) |

|

8010:03 |

Enable up/down counter |

Enablement of the up/down counter in place of the encoder with the bit set. Increments are counted at input A. Input B specifies the counting direction. |

BOOLEAN |

RW |

0x00 (0dec) |

|

8010:04 |

Gate polarity |

0: Disable gate 1: Enable pos. gate (gate locks with “HIGH” level) 2: Enable neg. gate (gate locks with “LOW” level) |

BIT2 |

RW |

0x01 (1dec) |

|

8010:08 |

Disable filter |

0: Activates the input filter (inputs A, /A, B, /B, C, /C only) 1: Deactivates the input filter If a filter is activated a signal edge must be present for at least 2.4 µs in order to be counted as an increment. |

BOOLEAN |

RW |

0x01 (1dec) |

|

8010:0A |

Enable micro increments |

If DC mode is activated, the AKT2G-ENC-190 interpolates micro-increments between the integer encoder increments. The lower 8 bits of the counter value are used in each case for the display. A 32-bit counter thus becomes a 24+8-bit counter, a 16-bit counter becomes an 8+8-bit counter. |

BOOLEAN |

RW |

0x00 (0dec) |

|

8010:0B |

Open circuit detection A |

An open circuit on track A is indicated in index 0x6010:07 and as process data. Diagnosis is only possible if the corresponding input is wired differentially. A differential voltage < 3.5 V (typical, subject to change) is detected as a broken wire. |

BOOLEAN |

RW |

0x01 (1dec) |

|

8010:0C |

Open circuit detection B |

An open circuit on track B is indicated in index 0x6010:07 and as process data. Diagnosis is only possible if the corresponding input is wired differentially. A differential voltage < 3.5 V (typical, subject to change) is detected as a broken wire. |

BOOLEAN |

RW |

0x01 (1dec) |

|

8010:0D |

Open circuit detection C |

An open circuit on track C is indicated in index 0x6010:07 and as process data. Diagnosis is only possible if the corresponding input is wired differentially. A differential voltage < 3.5 V (typical, subject to change) is detected as a broken wire. |

BOOLEAN |

RW |

0x00 (0dec) |

|

8010:0E |

Reversion of rotation |

Activates reversion of rotation |

BOOLEAN |

RW |

0x00 (0dec) |

|

8010:10 |

Extern reset polarity |

0: Fall (the counter is set to zero with a falling edge) 1: Rise (the counter is set to zero with a rising edge) |

BIT1 |

RW |

0x01 (1dec) |

|

8010:11 |

Frequency window |

This is the minimum time over which the frequency is determined. Default 10 ms [resolution: 1 µs] The number of pulses in the time window + the following is measured. The maximum waiting time is specified in the "Frequency Wait Time" parameter. The number of pulses is divided by the actual time window size. The determined frequency is output in index 0x6010:13 and as a process data. The frequency calculation is carried out locally without distributed clocks function. |

UINT16 |

RW |

0x2710 (10000dec) |

|

8010:13 |

Frequency scaling |

Scaling of the frequency measurement (must be divided by this value to obtain the unit in Hz): 100: “0.01 Hz” |

UINT16 |

RW |

0x0064 (100dec) |

|

8010:14 |

Period scaling |

Resolution of the period in the process data: 100: “100 ns” period value is a multiple of 100 ns 500: “500 ns” period value is a multiple of 500 ns |

UINT16 |

RW |

0x0064 (100dec) |

|

8010:15 |

Frequency resolution |

Resolution of the frequency measurement: 100: “0.01 Hz” |

UINT16 |

RW |

0x0064 (100dec) |

|

8010:16 |

Period resolution |

Internal resolution of the period measurement: 100: “100 ns” period value is a multiple of 100 ns The period is calculated internally with a resolution of 100 ns. The max. measurable period can then be approx. 1.6 seconds. 500: “500 ns” period value is a multiple of 500 ns Internally the period is calculated with 500 ns resolution. The maximum measurable period is approx. 32.7 ms. The resolution of process data continues to be the value according to index 0x8010:14 (e.g. 100 ns [default]). |

UINT16 |

RW |

0x01F4 (500dec) |

|

8010:17 |

Frequency Wait Time |

Waiting time [ms] for frequency measurement Once the time specified in the frequency window has elapsed, the system waits for the next positive edge from track A. This enables the update speed for the Frequency process data to be optimized, depending on the expected frequencies. At least double the period of the minimum frequency to be measured should be entered here. t >= 2* (1 / fmin) |

UINT16 |

RW |

0x0640 (1600dec) |

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

6010:0 |

ENC Inputs |

Maximum subindex |

UINT8 |

RO |

0x16 (22dec) |

|

6010:01 |

Latch C valid |

The counter value was locked with the “C” input. The data with index 0x6010:12 match the latched value when the bit is set. To reactivate the latch input, index 0x7010:01 must be cancelled and then reset. |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:02 |

Latch extern valid |

The counter value was locked via the external latch. The data with index 0x6010:12 match the latched value when the bit is set. To reactivate the latch input, index 0x7000:02 or object index 0x7000:04 must be cancelled and then reset. |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:03 |

Set counter done |

The counter was set. |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:04 |

Counter underflow |

Counter underflow. Overflow/underflow control is inactive in combination with a reset function (C/external). |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:05 |

Counter overflow |

Counter overflow. Overflow/underflow control is inactive in combination with a reset function (C/external). |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:06 |

Status of input status |

State of the status input (alarm “input 1”) |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:07 |

Open circuit |

Indicates an open circuit. Configuration via index 0x8010:0A, 0x8010:0B, 0x8010:0C |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:08 |

Extrapolation stall |

The extrapolated part of the counter is invalid |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:09 |

Status of input A |

Status of input A |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:0A |

Status of input B |

Status of input B |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:0B |

Status of input C |

Status of input C |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:0C |

Status of input gate |

The state of the gate input |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:0D |

Status of extern latch |

Status of the extern latch input |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:0E |

Sync Error |

The Sync error bit is only required for DC mode. It indicates whether a synchronization error has occurred during the previous cycle. This means a SYNC signal was triggered in the AKT2G-ENC-190, although no new process data were available (0=OK, 1=NOK). |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:0F |

TxPDO State |

Validity of the data of the associated TxPDO (0 = valid, 1 = invalid). |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:10 |

TxPDO Toggle |

The TxPDO toggle is toggled by the slave when the data of the associated TxPDO is updated. |

BOOLEAN |

RO |

0x00 (0dec) |

|

6010:11 |

Counter value |

Counter value |

UINT32 |

RO |

0x00000000 (0dec) |

|

6010:12 |

Latch value |

Latch value |

UINT32 |

RO |

0x00000000 (0dec) |

|

6010:13 |

Frequency value |

The frequency (setting of the scaling and resolution in index 0x8010:13 and 0x8010:15) |

UINT32 |

RO |

0x00000000 (0dec) |

|

6010:14 |

Period value |

The period (setting of the scaling and resolution in index 0x8010:14 and 0x8010:16) |

UINT32 |

RO |

0x00000000 (0dec) |

|

6010:16 |

Timestamp |

Timestamp of the last counter change |

UINT64 |

RO |

|

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

7010:0 |

ENC Outputs |

Maximum subindex |

UINT8 |

RO |

0x11 (17dec) |

|

7010:01 |

Enable latch C |

Activate latching via input “C”. |

BOOLEAN |

RO |

0x00 (0dec) |

|

7010:02 |

Enable latch extern on positive edge |

Activate external latch with positive edge. |

BOOLEAN |

RO |

0x00 (0dec) |

|

7010:03 |

Set counter |

Set counter |

BOOLEAN |

RO |

0x00 (0dec) |

|

7010:04 |

Enable latch extern on negative edge |

Activate external latch with negative edge. |

BOOLEAN |

RO |

0x00 (0dec) |

|

7010:11 |

Set counter value |

The counter value to be set via “Set counter” (index 0x7010:03). |

UINT32 |

RO |

0x00000000 (0dec) |

Information / Diagnostic Data (Channel Specific)

| Index (hex) | Name | Meaning | Data type | Flags | Default |

|---|---|---|---|---|---|

|

A010:0 |

ENC Diag data |

Maximum subindex |

UINT8 |

RO |

0x03 (3dec) |

|

A010:01 |

Open circuit A |

Open circuit on track A |

BOOLEAN |

RO |

0x00 (0dec) |

|

A010:02 |

Open circuit B |

Open circuit on track B |

BOOLEAN |

RO |

0x00 (0dec) |

|

A010:03 |

Open circuit C |

Open circuit on track C |

BOOLEAN |

RO |

0x00 (0dec) |

Single-ended connection for TTL encoder

In addition to encoders with differential RS422 interface, single-ended encoders with TTL interface are also supported. Please note the following:

- Operating mode selection encoder "0x80n0:03 Enable up/down counter = FALSE".

- The differential inputs (/A, /B, /C) must remain open and must not be connected to ground

- The option to reverse the direction of rotation is given by setting the bit in index 0x80n0:0E "reversion of rotation =TRUE".

- The open circuit detection does not work in principle conditionally with single-ended connection