Master Configuration

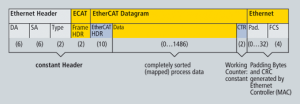

EtherCAT communicates a maximum of 1486 bytes of distributed process data with just one Ethernet frame.

- Unlike other solutions where the master device in each network cycle has to process, send, and receive frames for each node, EtherCAT systems typically only need one or two frames per cycle for the entire communication with all nodes.

- EtherCAT masters do not require a dedicated communication processor.

- The master functionality puts hardly any load on the host CPU, which can handle this task easily while processing the application program.

- EtherCAT can be implemented without special or expensive active plug-in cards, just by using a passive NIC card or the on-board Ethernet MAC.

- Implementation of an EtherCAT master is very easy, particularly for small and medium-sized control systems and for clearly defined applications.

Example

- A PLC with a single process image: if it does not exceed the 1486 bytes, cyclic sending of a single Ethernet frame with the cycle time of the PLC is sufficient.

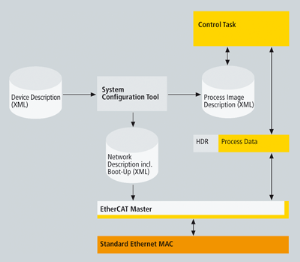

- See Figure: "Master-Implementation with One Process Image" for more information.

- Because the header does not change at run-time, the only thing required is that a constant header be added to the process image and that the result be transferred to the Ethernet controller.

- The process image is already sorted, since with EtherCAT mapping does not occur in the master, but in the slaves - the peripheral devices insert their data at the respective points in the passing frame.

- This further unburdens the host CPU.

- It was found that an EtherCAT master entirely implemented in software on the host CPU uses less of its processing power than much slower fieldbus systems implemented with active plug-in cards.

- Servicing the DPRAM of the active card alone puts more load on the host.

System configuration tools provide the network and device parameters (including the corresponding boot-up sequence) in a standardized XML format.

See Configure EtherCAT Motion Bus for more information.

Figure 1: Master-Implementation with One Process Image